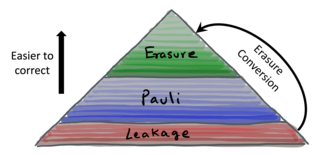

Hierarchy of errors: Leakage errors (out of the code space) are the most dangerous, but dual-rail qubits can raise a flag to convert them to erasures.

Quantum computers have the potential to create a revolutionary form of information processing, however current hardware is very prone to errors. A grand challenge is to learn how to correct these errors so that we can build large-scale fault-tolerant quantum computers. The ERASE project will establish a NSF Quantum Testbed to answer this challenge by developing an innovative quantum computing platform based on ‘erasure flag’ qubits that herald when and where errors occur. Erasure flag information will make it easier to correct the errors and achieve fault tolerance. Researchers will have access to advanced tools for developing new algorithms and improving software systems, as well as the opportunity to experiment with quantum error correction and create new quantum algorithms that use mid-circuit measurements and program branching (decision making) based on the measurement results. ERASE is a collaboration between academia and an industrial hardware partner, Quantum Circuits, Inc. (QCI), to drive research towards practical quantum information technologies. ERASE will promote educational initiatives to cultivate a skilled quantum workforce, in partnership with historically Black colleges and universities. The aim is to build a vibrant national ecosystem for quantum research, paving the way toward achieving quantum advantage in computation and simulation.

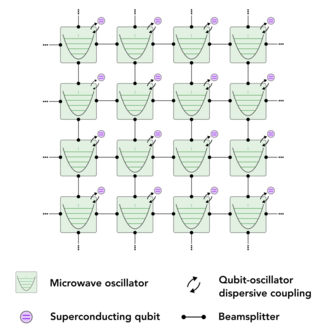

Schematic hardware layout of dual-resonator architecture. Neigh-boring pairs of resonators form dual-rail error-flag qubits.

Our goal is to deploy novel high performance superconducting hardware whose logical qubit states are defined by a single microwave photon shared between two long-lived resonators. This dual-resonator (‘dual-rail’) logical encoding can detect the dominant error (photon loss) converting leakage out of the code space into a flagged erasure error. Concatenating this dual-rail error detection code into a larger code will allow efficient correction of the dominant errors since their locations are flagged. Because our proposed architecture has unique hardware characteristics, it will enable new types of algorithms and require a rethinking of the systems software toolflow. We will form a national community of researchers in applications/algorithms, software, and systems architecture to develop a NSF Quantum Testbed in collaboration with our hardware partner, QCI. QCI will provide researchers with access to this new computational paradigm through an Application Programming Interface (API) into multiple levels of the system stack to: (1) develop and execute new algorithms designed for the error-detecting and error-correcting capabilities of our novel superconducting quantum computing testbed; (2) contribute to improved middleware design (e.g., error-aware compilers; efficient control flow for mid-circuit measurements and feedforward); (3) co-design of improvements in error correction protocols.